INTRODUCTION

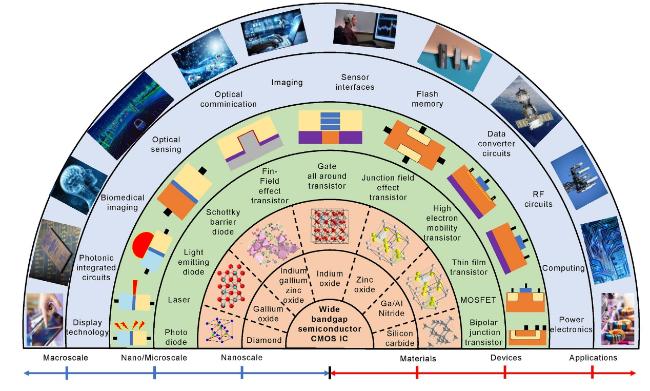

Fig. 1. Detailed summary of wide bandgap semiconductors based on materials, devices, and application perspective. |

Table 1. Properties of wide bandgap semiconductors. |

| Property | 4H-SiC | GaN | ZnO | In2O3 | IGZO | Ga2O3 | Diamond | AlN |

|---|---|---|---|---|---|---|---|---|

| Bandgap (eV) | 3.3 | 3.4 | 3.37 | 3.7 | 3.5 | 4.9 | 5.5 | 6.0 |

| Breakdown field (MV/cm) | 3.1 | 4.9 | 0.01 | NA | 2.7 | 10.3 | 4.4 | 15.4 |

| Sat. velocity (107 cm/s) | 2.2 | 1.4 | 3.2 | 0.25 | 0.8 | 1.8 | 1.5 | 1.6 |

| Thermal conductivity (W mK−1) | 490 | 230 | 50 | 2.2 | 1.4 | 13 | 2200 | 320 |

| Johnson FOM ratio vs Si | 278 | 1089 | NA | NA | NA | 2844 | 81 000 | 7744 |

| Baliga FOM ratio vs Si | 712 | 3170 | 10 | NA | 3.7 | 4125 | 62 954 | 38 181 |

| Tunneling eff. mass (mo) | NA | 0.15 | 0.24 | 0.40 | 0.34 | 0.31 | 0.69 | NA |

| Melting point (°C) | 2730 | 2500 | 1975 | 1910 | 850 | 1700 | 3550 | 2830 |

| Thermal budget | High | High | Low | Low | Low | High | High | High |

| CMOS demonstration status | Cree 2006 | HRL 2016 | NA | NA | NA | NA | NA | NA |

OVERVIEW OF DIGITAL INTEGRATED CIRCUITS

Logic gates

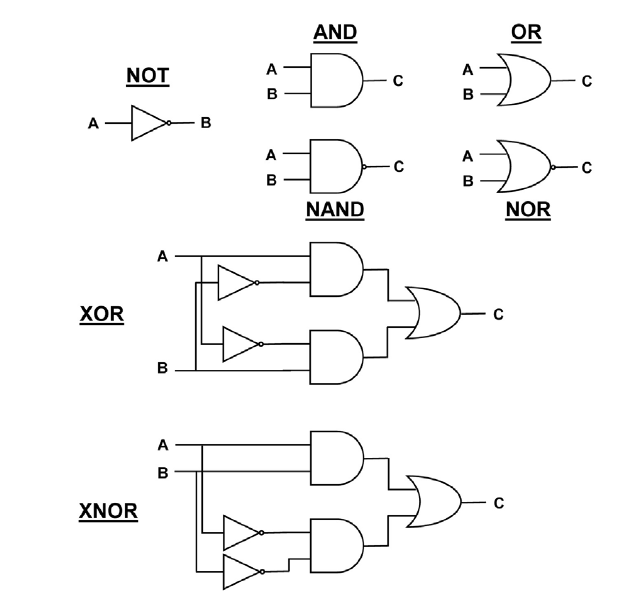

Fig. 2. Summary of logic gates including NOT, AND, NAND, OR, NOR, XOR, and XNOR equivalent circuits. |

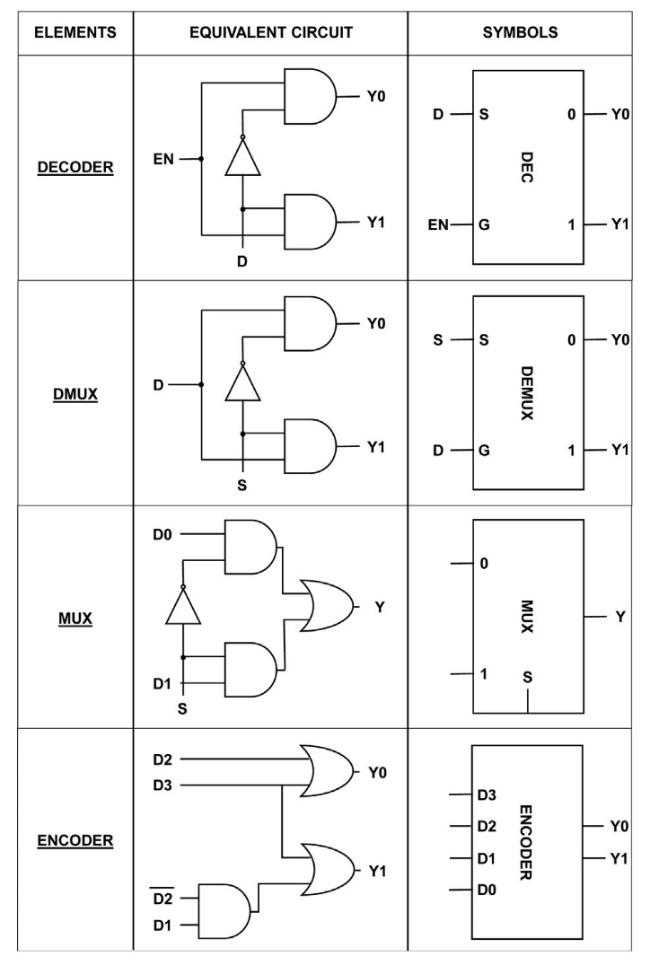

Decoder and demultiplexer

Fig. 3. Summary of logic circuits such as decoders, demultiplexers, multiplexers, and encoders. |

Multiplexer

Encoder

MATETIAL PROPERTIES OF WBG SEMICONDUCTORS

Gallium nitride (GaN)

Zinc oxide (ZnO)

Indium oxide (In2O3)

IGZO

Gallium oxide (Ga2O3)

Diamond

SINGLE CRYSTALLINE WBG SEMICONDUCTOR-BASED DEVICES AND CIRCUITS

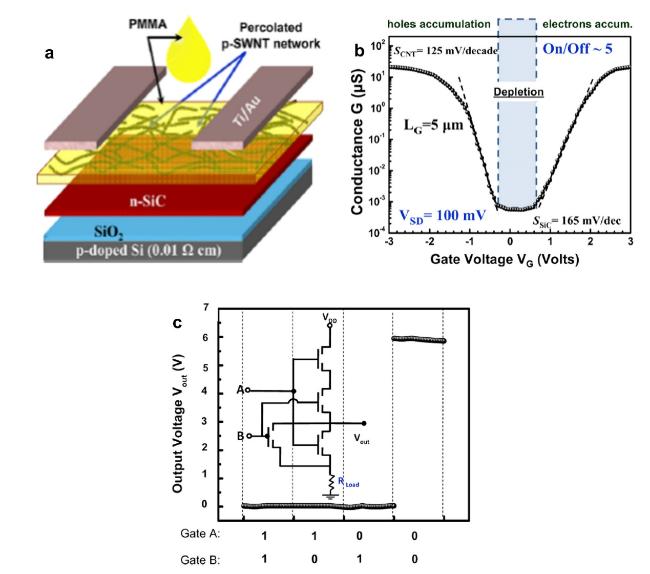

Fig. 4. a, Schematic illustration and b, Electrical characteristics of SiC-based bottom-gate device. c, Output characteristics of NOR gate circuit. Reprinted with permission from ref.159. © 2012 American Institute of Physics. |

GaN logic circuits

Ga2O3

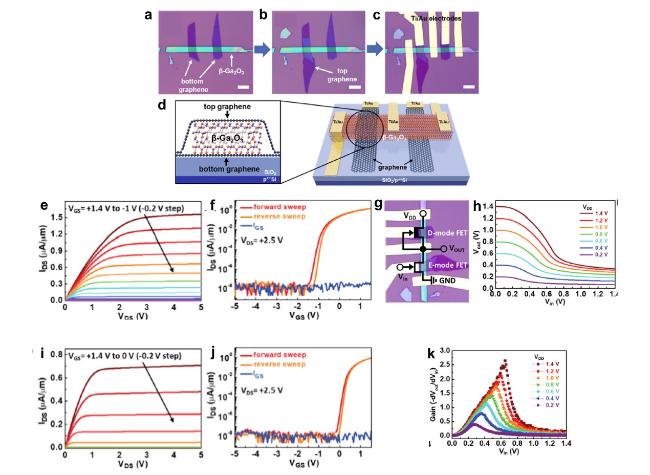

Fig. 5. a-c, Optical micrograph and d, schematic illustration of β-Ga2O3 MESFET device. Electrical characteristics of e-f, single-gate and g-h, dual-gate MESFET device. i-k, Electrical characteristics of β-Ga2O3 NMOS logic inverter circuit. Reprinted with permission from ref.183. © 2020 American Chemical Society. |

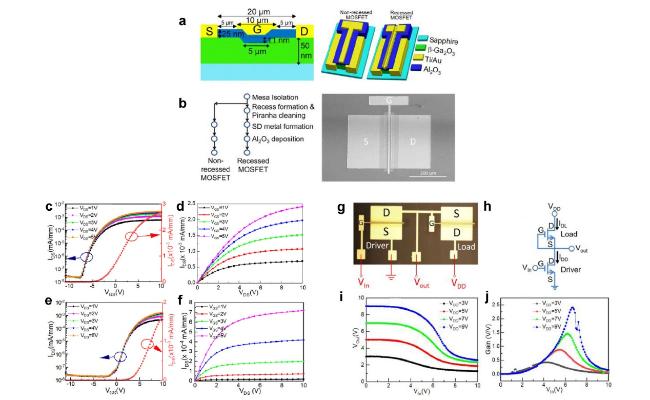

Fig. 6. a, Schematic illustration, b, Fabrication process and b-right, SEM image of β-Ga2O3 TFT device. c-f, Transfer and output characteristics of β-Ga2O3 TFT device. g, Optical micrograph, h, Circuit diagram, and i-j, Electrical characteristics of logic inverter circuit. Reprinted with permission from ref.186. © 2023 American Institute of Physics. |

Diamond

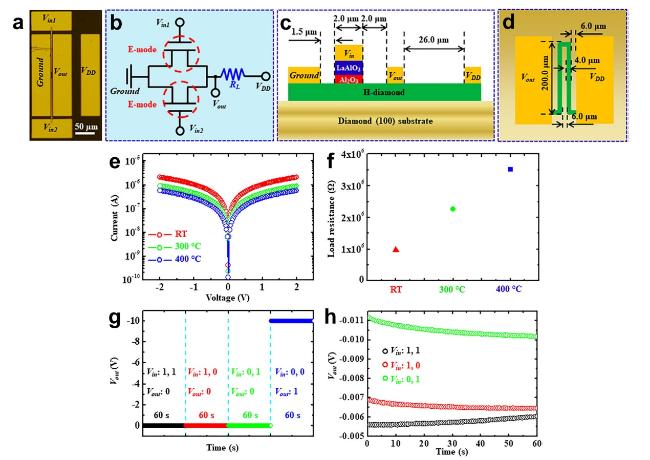

Fig. 7. a, Optical micrograph, b, Circuit diagram and c-d, Schematic illustration of diamond-based NOR logic circuit. e- f, I-V characteristics of diamond TFT device. g-h, Electrical characteristics of NOR logic circuit. Reprinted with permission from ref.201. © 2018 American Institute of Physics. |

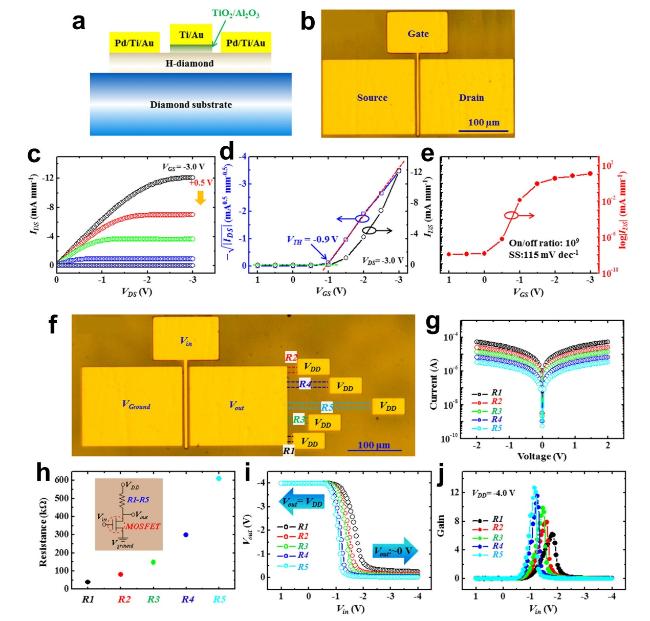

Fig. 8. a, Schematic illustration, b, Optical micrograph, and c-e, Electrical characteristics of diamond-based MOSFET device. f, Optical micrograph of diamond logic inverter connected to different load resistors. g-j, Electrical characteristics of diamond logic inverter circuit. Reprinted with permission from ref.203. © 2017 American Institute of Physics. |

Fig. 9. a, Schematic illustration of diamond based diode device. Output characteristics of OR gate designed by diode having b, 125, c, 325, and d, 9360-finges. Reprinted with permission from ref.206. © 2012 Elsevier BV. |

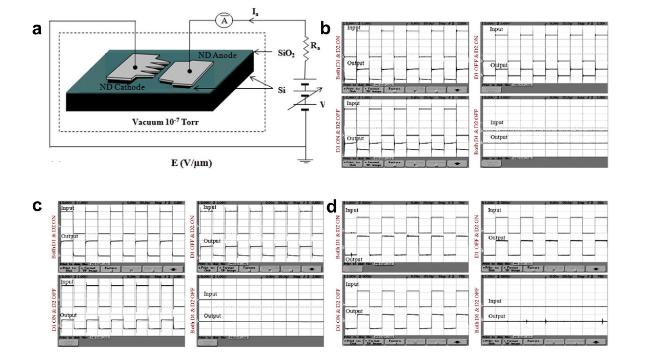

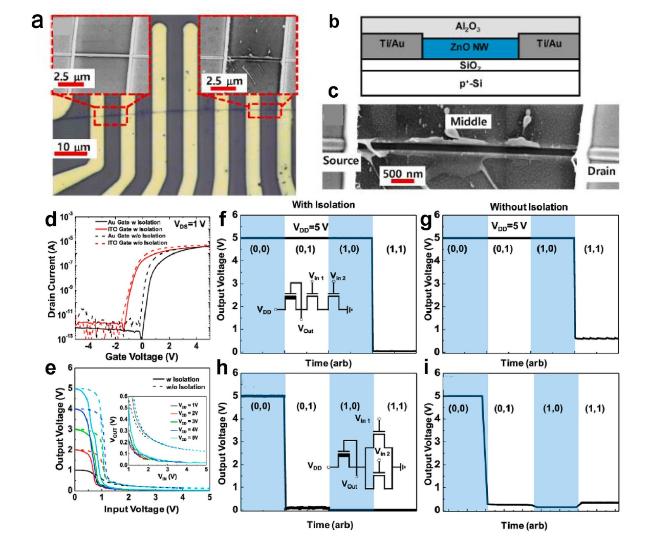

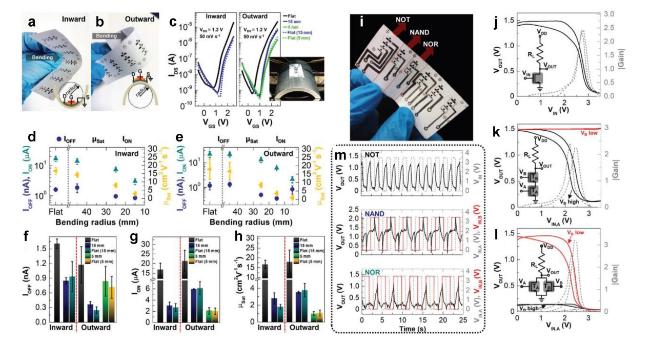

THIN FILM WBG SEMICONDUCTOR-BASED DEVICES AND LOGIC CIRCUITS

Fig. 10. a, Optical micrograph, b, Cross sectional image, c, SEM image of the ZnO-based NW device. d, Transfer characteristics of ZnO transistor. Output characteristics of ZnO-based e, inverter, f-g, NAND, and h-i, NOR logic circuit. Reprinted with permission from ref.214. © 2020 Elsevier B.V. |

Fig. 11. a-b, Mechanical bending studies, c-e, Electrical characteristics and f-h, Transistor parameter analysis of ZnO-based TFT device. i, Optical image of ZnO-based flexible circuit. Output characteristics of j, NOT, k, NAND, and l, NOR circuit. m, Dynamic characteristics of NOT, NAND, and NOR circuits. Reprinted with permission from ref.215. © 2021 Wiley-VCH. |

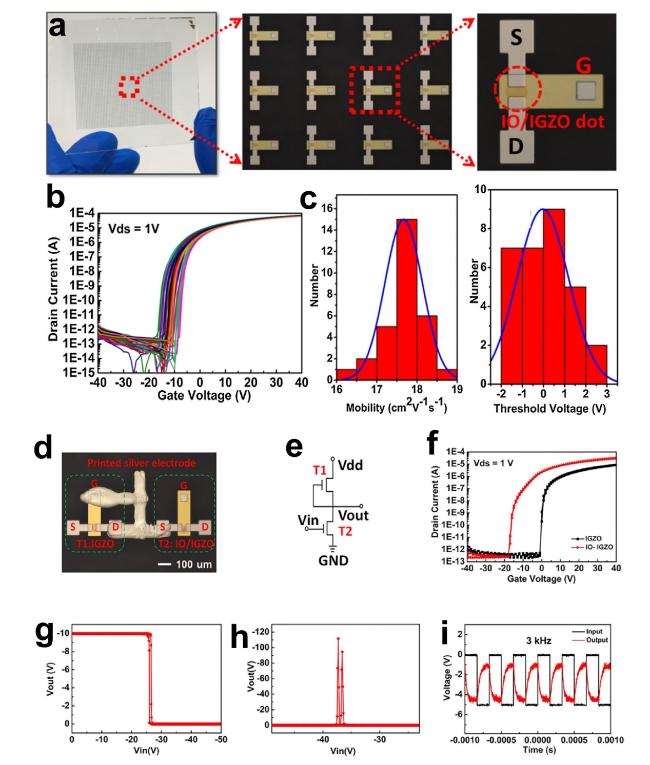

In2O3

Fig. 12. a, Optical micrograph, b, electrical characteristics, and c, transistor parameters of IGZO TFT devices. d, Optical micrograph and e-i, electrical characteristics of IGZO-based NMOS inverter circuit. Reprinted with permission from ref.226. © 2021 Elsevier B.V. |

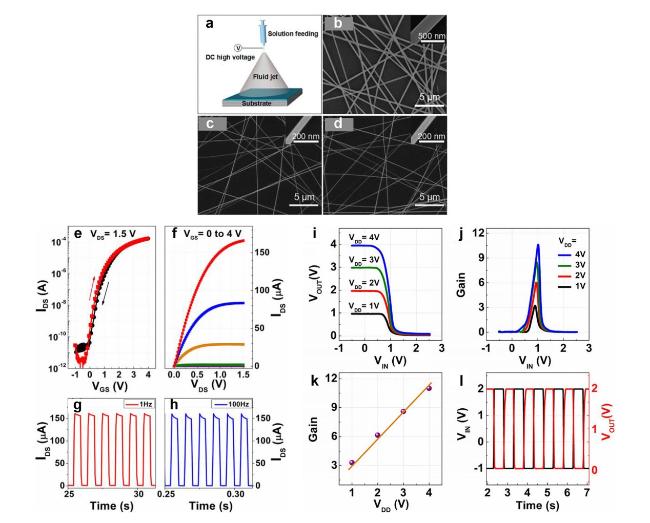

Fig. 13. a, Schematic illustration and b-d, SEM images of In2O3-based TFT device. e-f, Electrical characteristics and g-h, Dynamic response of the In2O3 TFT device. i, Output characteristics, j-k, Gain behavior and l, Dynamic response of the In2O3-based logic inverter circuit. Reprinted with permission from ref.228. © 2018 American Institute of Physics. |

IGZO

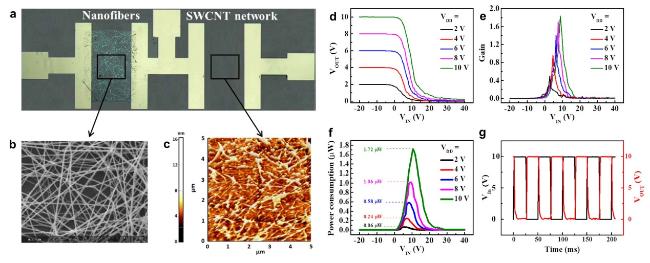

Fig. 14. a, Optical micrograph of the as-fabricated inverter circuit with insets, b, SEM and c, AFM image of the IGZO nanofibers. d, VTC, e, Gain, f, Power consumption, and g, Switching behavior of the inverter circuit. Reprinted with permission from ref.240. © 2018 American Institute of Physics. |

SUMMARY AND PERSPECTIVES

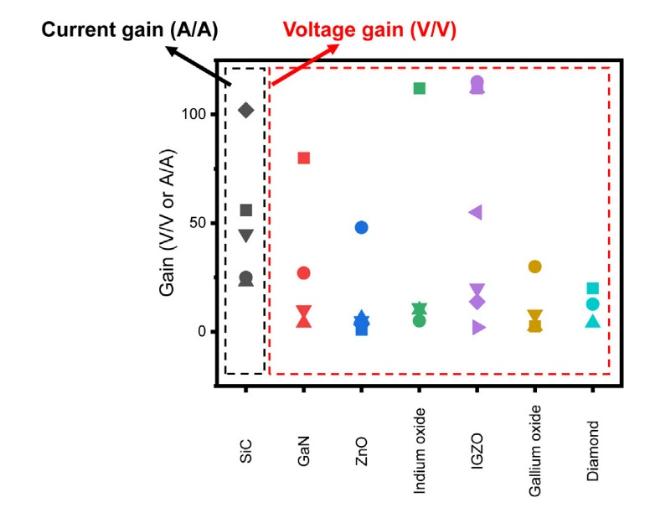

Overview of WBG devices-based inverter performance

Fig. 15. Summary of current (A/A) and voltage (V/V) inverter gain of different wide bandgap semiconductors. |