INTRODUCTION

RESULTS AND DISCUSSIONS

Full vdW-FeFET

Voltage-pulse controlled partial polarization of multi-domain ferroelectric

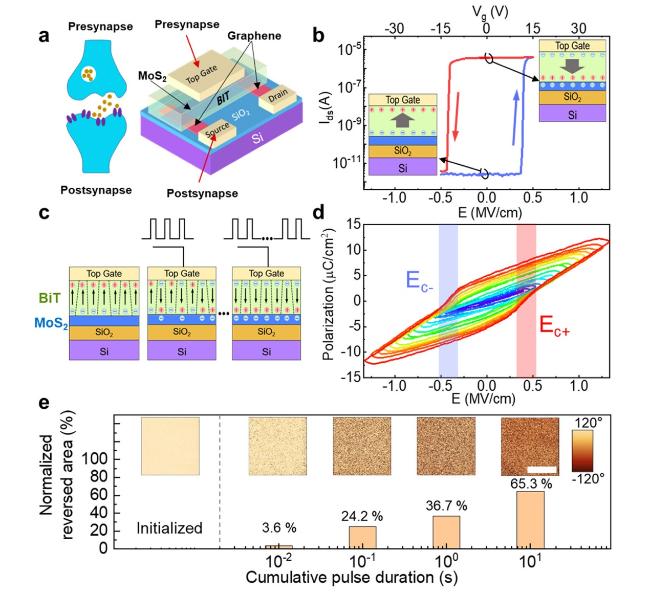

Fig. 1. vdW-FeFET artificial synaptic device and the partial polarization reversal of multi-domain BiT. a, Schematic illustration of the vdW-FeFET synaptic device. b, Ids-Vg transfer characteristic measured in vdW-FeFET. The source-drain bias Vds = 100 mV. Inset: Schematics of the full polarizations of FE in the on-state and off-state. c, Schematic of multi-domain and partial FE-polarization switching in vdW-FeFET. d, The P-V curves were measured using an metal-ferroelectric-metal (MFM) device. The blue and red shadows indicate the distributions of the coercive fields in the up-and-down polarization. e, The partial polarization reversal probed by the PFM technique and the corresponding reversed area at specific cumulative pulse durations extracted from the PFM images. The scale bar is 1 µm. |

Programming of multi-state FeFET memory

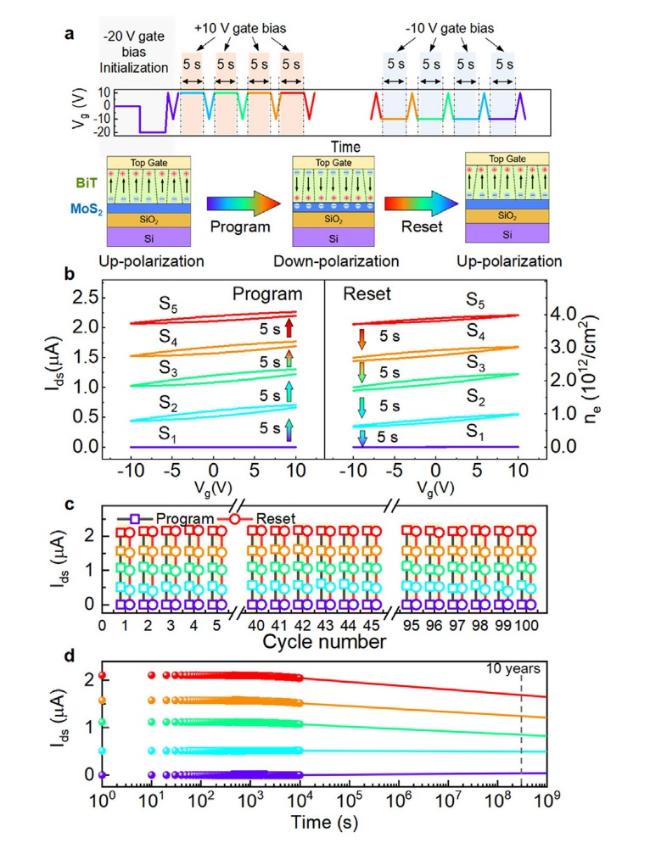

Fig. 2. Gate bias programmed multi-states characteristics. a, Schematic illustration of the program/reset sequence in the measurement (top) and gate bias duration induced partial polarization of ferroelectric domains in vdW-FeFET (bottom). b, Ids-Vg characteristics measured after 5 to 20 s of the program (left) and the reset (right) sequence with a step of 5 s in bias duration. c, Ids read at Vg = 0 V, Vds = 100 mV in the 100 program/reset cycles. d, The retention characteristic of S1 to S5. |

High-performance artificial synapse

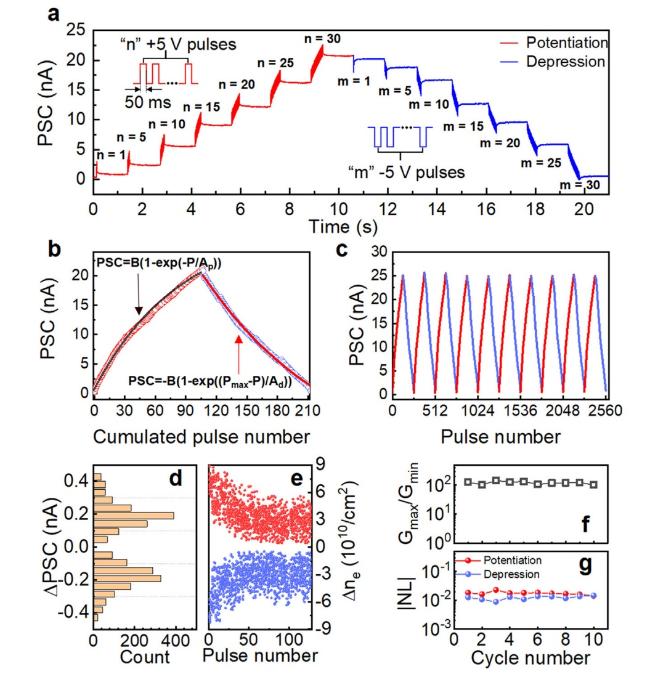

Fig. 3. Synaptic performance of vdW-FeFET. a, The PSC weight during potentiation (red) and depression processes. “n” denotes the number of pulses of individual potentiation and depression pulse train. b, Non-linearity factor fitting with summarized PSC weight update in a. c, Cycle-to-cycle potentiation and depression with 128 conductance states. d, Count distribution of PSC and ne change (ΔPSC and Δne). e, ΔPSC and Δne variation in the cycle-to-cycle weight update measurement. f, The dynamic range Gmax/Gmin and g, the non-linearity |NL| variation extracted from c. The Vds is set to 1 mV during these measurements. |

Pattern recognition using vdW-FeFET-based artificial neural network

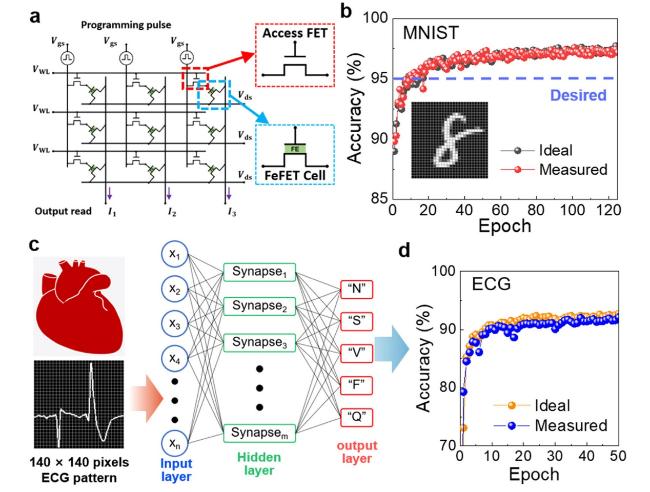

Fig. 4. MNIST digits and ECG pattern recognition. a, The structure of the vdW-FeFET-based pseudo-crossbar array used to build the artificial neural network. b, The MNIST recognition accuracy as a function of training epochs. c, The schematic of the neural network used for ECG pattern recognition simulation. d, The accuracy of ECG pattern recognition simulation as a function of training epochs. |

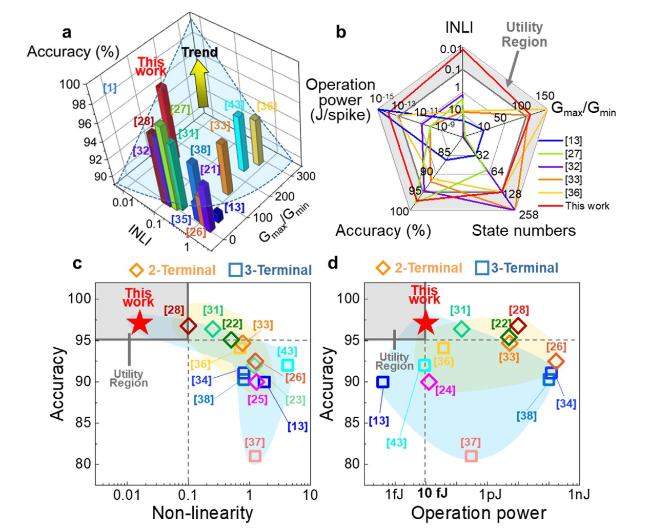

Metric benchmarking of recent advances

Fig. 5. Metrics benchmarking of the recently developed synaptic devices. a, An empirical roadmap of the trend to achieve higher accuracy. b, Radar plot of our vdW-FeFET device performance results compared with state-of-the-art synaptic devices. c-d,present the overall metrics benchmarking of the latest synaptic devices in different references in terms of accuracy, non-linearity, and operation power. The empty diamonds denote two-terminal devices, and squares denote three-terminal devices, respectively. |