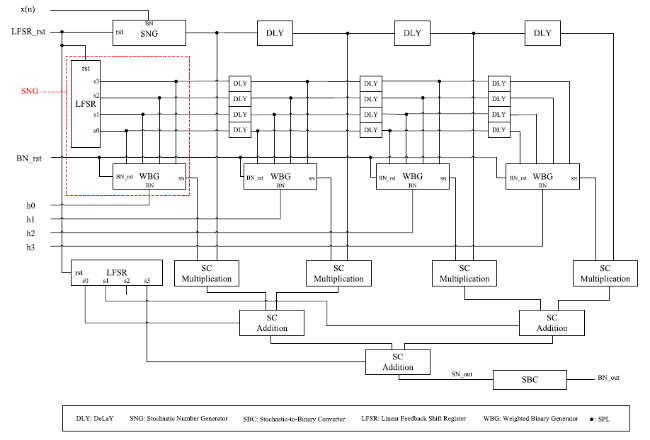

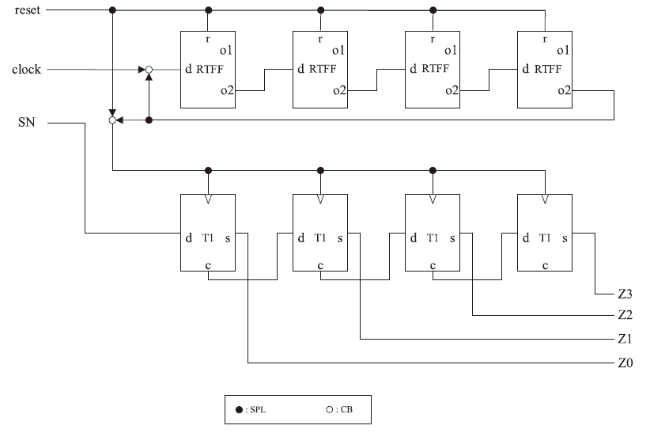

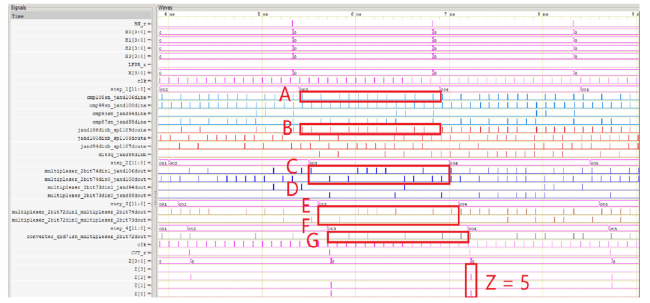

To verify the functionality of the whole design, we have defined several test benches for the proposed FIR filter. Take the calculating path of the parameter

h 0 as an example to analyze the correctness of the entire circuit. For the convenience of description, the data flow through the path is marked as “A”, “B”, “C”, “D”, “E”, “F”, and “G”, as shown in

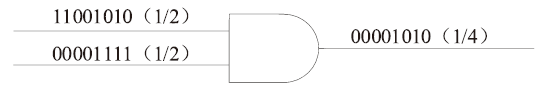

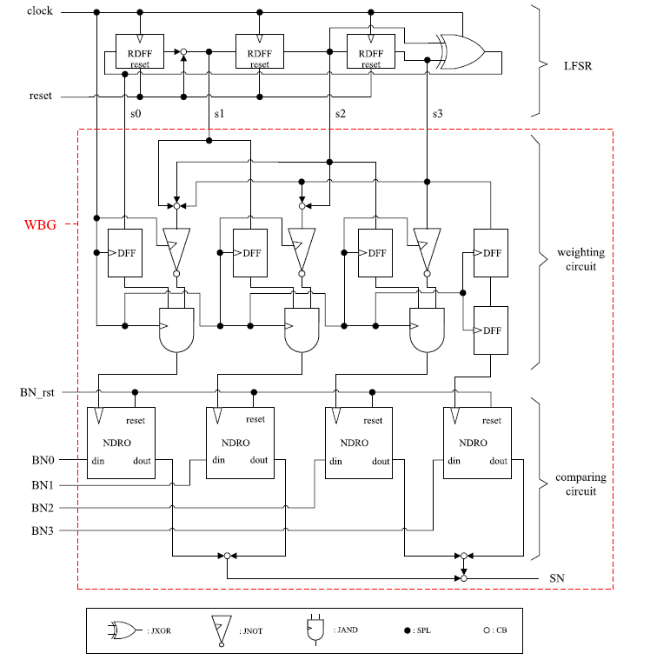

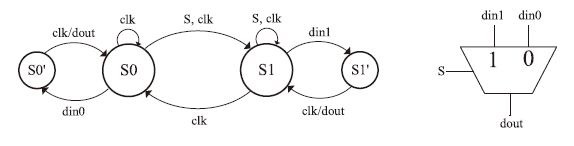

Fig. 9. The values of “A” and “B” are 11/15 (101011111101101) and 10/15 (110101111010110), after the multiplier operation (AND gate), “C” is obtained, and its value is 6/15 (100001111000100). “D” (6/15, 001010000011011) is also the output from another multiplier. “C” and “D” are added (scaled addition) to obtain “E” with a value of 6/15 (000011101000101). Similarly, “E” and “F” (1/15, 001000000000000) are scaled-added to obtain “G” (5/15, 001010001000101), and SBC counts “G”. Finally, Z = 0101 (i.e. G = 5/15, 001010001000101) is output, due to the imprecise property of SC. The results show that the proposed FIR filter works correctly at 10 GHz (see

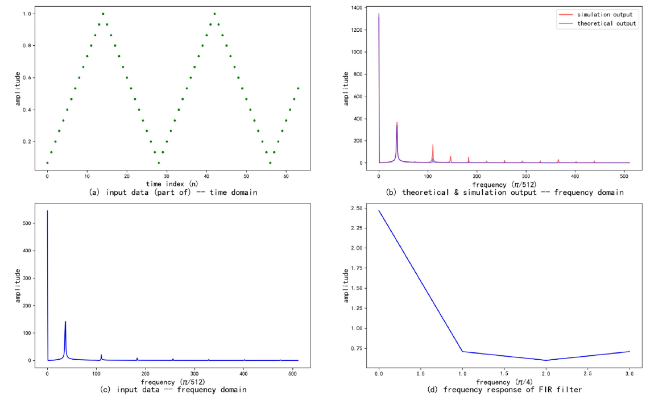

Fig. 10).